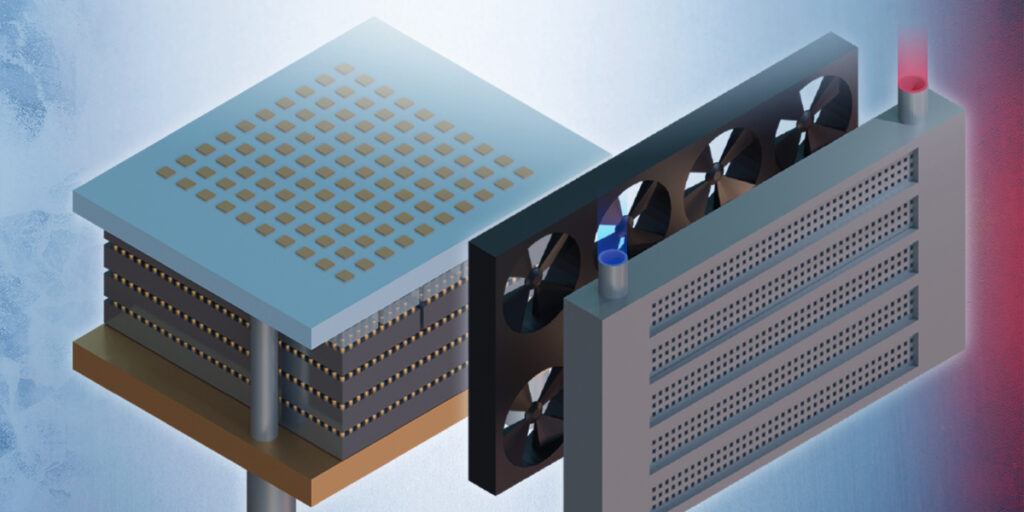

HRL Laboratories plans to develop a superior cooling system for stacks of microelectronic chips and surpass heat transfer metrics set out by DARPA. The program aims to create compact thermal management technology in a chip stack using 3D Heterogeneous Integration (3DHI). (Graphic: Business Wire)

MALIBU, Calif.—HRL Laboratories is working to surpass heat transfer metrics set out by the Defense Advanced Research Project Agency (DARPA) with a novel cooling system for stacks of microelectronic chips.

The program, called PHased ARray with INnovative HEterogeneously Integrated Thermal Solution (PHARINHEITS), aims to create compact thermal management technology in a chip stack using 3D heterogeneous integration (3DHI), according to a release from HRL Laboratories.

By partnering with premier university labs, HRL is uniting experts in heat transfer technologies, Si CMOS, GaN, heterogeneous integration, and RF front-ends. Under the leadership of Professor Michael Ohadi, for example, the University of Maryland is focused on developing high-performance, bottom-of-stack microchannel thermal technology, as well as fabricating compact, additively manufactured heat exchangers.

At the same time, Stanford University is focused on developing multifunctional top-of-stack microchannel thermal technology under the leadership of Adjunct Professor Mehdi Asheghi and Professor Ken Goodson. Purdue University is working on reliability engineering and thermomechanical modeling under the leadership of Professors Ganesh Subbarayan and Shubhra Bansal. And MIT Lincoln Laboratory is focusing on silicon chip design and fabrication under the leadership of Chenson Chen, Ph.D., and Ryan Keech, Ph.D., the release stated.

Meanwhile, HRL Laboratories is directing the overall program, leading the system design, developing thermal isolation and thermal spreading techniques, leading the 3D integration, and executing system performance testing.

“HRL’s experience in 3D integration is crucial to the disparate chips and cooling systems working together in a tightly coupled package,” said Christopher Roper, principal investigator at HRL, in the release. “The challenge in cooling this 3DHI stack of chips is local heat density. We need to cool the heat equivalent of more than 190 laptop CPUs, but in the size of a single CPU package.”

By surpassing current integrated thermal management limits, the PHARINHEITS program is expected to enable next-generation millimeter-wave (mm wave) radio frequency phased arrays with dramatically increased transmit power relative to current systems. These stacked chips may be used in future phased array radar and communication systems with increased range, the release said.

Inadequate integrated thermal management is a limiting factor in the continued maturation of compact high-performance microsystems. 3DHI chip stacks, for example, are more compact, allowing for faster, smaller, and lighter phased arrays. However, the challenge has traditionally been how to disperse the heat that they generate. That’s because the thicker die stack—with its additional internal thermal interfaces—inhibits heat flow, according to HRL.

This challenge has limited the growth of system capabilities in size, weight, and power (SWaP) constrained applications. This is particularly true in radio frequency systems, image analysis, and high-performance computing, including artificial intelligence and machine learning applications.

Recently, DARPA set forth a set of metrics around how much thermal dissipation is required. These are the goals that HRL Laboratories and its university partners are planning to surpass, according to the release.

A private company owned jointly by Boeing and GM, HRL Laboratories, LLC, California (www.hrl.com) is dedicated to pioneering the next frontiers of physical and information science. The company works to deliver transformative technologies in automotive, aerospace and defense.